Deca Technologies, a U.S. advanced wafer and panel level packaging technology company, is partnering with Arizona State University (ASU) to create North America's first Fan-Out Wafer-Level Packaging (FOWLP) Research and Development Center, with the aim of fostering U.S.-based packaging technology innovations as well as expanding semiconductor fabrication capabilities to drive advances in cutting-edge areas such as artificial intelligence, machine learning, automotive electronics and high-performance computing (HPC). and high-performance computing (HPC), among other cutting-edge fields.

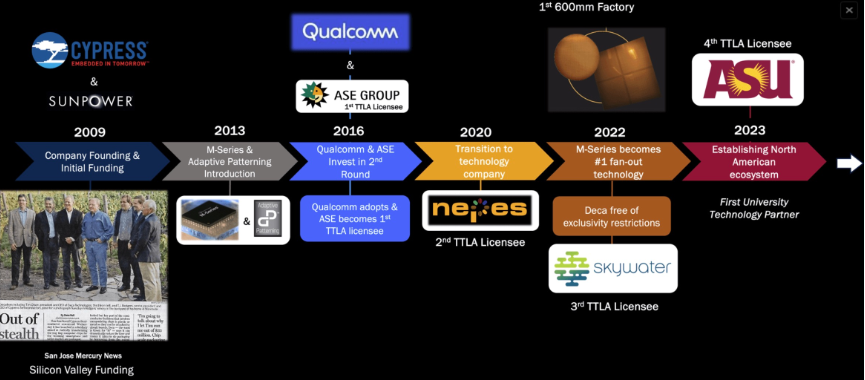

Founded in 2009, Deca Technologies is an electronic interconnect solutions provider offering wafer-level packaging (WLP) services to the semiconductor industry.

Arizona State University's Center for Advanced Wafer-Level Packaging Applications and Development is said to combine state-of-the-art advanced packaging technologies, equipment, processes, materials, expertise and training to facilitate the development of new capabilities from proof-of-concept to pilot scale.

ASU is the first university in the U.S. to implement Deca's M-Series fan-out packaging technology and adaptive patterning technology under the Microelectronics Commons, a network of regional technology centers that coordinates the delivery of projects requested by the Department of Defense as part of the Chip and Science Act, federal legislation aimed at expanding U.S. global leadership in microelectronics.

ASU's partnership with Deca is dedicated to building advanced packaging capabilities on a local level. To achieve this goal, the center will require the purchase and installation of a full suite of process and metrology equipment at the facility, capable of compatibility with 200mm and 300nmm wafer sizes, as well as 300mm M-Series fan-out wafers, providing unmatched flexibility for a variety of customers and applications.

The new center will also include the integration of ASU's Macro Technology Works Center at the Arizona State University Research Park in Tempe, further providing additional technical capabilities to advance projects within the ASU-led Southwest Center for Advanced Prototyping (SWAP), part of the Microelectronics Shared Center.

The partnership also provides labor talent development opportunities for ASU faculty, staff and students to participate in ongoing projects to train semiconductor technicians who are increasingly in demand from Intel, TSMC, Amgen and many other semiconductor companies clustered in Phoenix, Arizona.

Deca's 1st Generation M-Series FOWLPs are widely used in the world's leading smartphones, with the 1M-Series being the highest shipped fan-out technology, with over 5 billion devices based on the technology. The 2nd generation M-Series includes adaptive patterning technology that brings unprecedented higher density scaling for heterogeneous integration and chiplet applications.

Wishlist (0 Items)

Wishlist (0 Items)